Verilog-1995和verilog-2001的区别和改进

2024-11-03 00:16:26

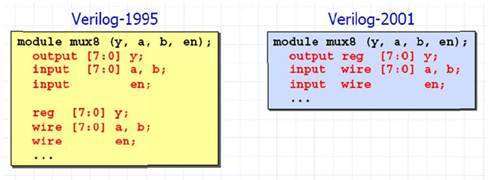

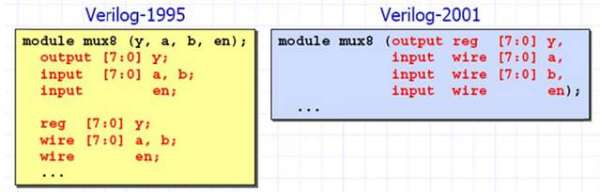

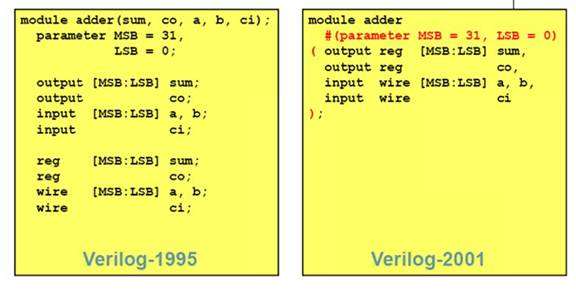

1、模块声明的扩展

(1) Verilog‐2001允许将端口声明和数据类型声明放在同一条语句中,例子如下:

(2)Verilog‐2001中增加了ANSIC风格的输入输出端口声明,可以用于module,task和function。例子如下:

(3)对于含有parameter的module,例子如下:

2、带有初始化的寄存器类型变量声明

Verilog‐2001中允许在声明变量的同时对其进行初始化赋值,他是在initial语句中的0时刻开始执行。例子如下:

3、敏感表的改进

(1)逗号分开敏感列表

在敏感表中的变量可以用逗号“,”分开,当然,当然or也是可以的。例子如下:

always@(posedge clk,negedge rst)也是可以的。

(2)组合逻辑的电平敏感@* //@(*) is also ok

“*”代表了逻辑块中每个被赋值的变量,例子如下:

4、有符号算数运算的扩展

(1)net型和reg型可以声明为带符号的变量

(2)函数的返回值可以是有符号数

(3)Literal integer numbers可以定义为有符号的

(4)增加算数右移左移(>>>,<<<)

操作符“>>>”和“<<<”。对于有符号数,执行算术移位操作时,将符号位填补移出的位。例子如下:

(5)增加系统函数$signed,$unsigned

用于在无符号和有符号数之间的转换

5、可变向量域的选择

[<starting_bit>+”:width]从起始位开始递增,位宽为width

[<starting_bit>‐”:width]从起始位开始递减,位宽为width

其中,起始位可以是变量,但位宽必须是整数。因此可以用可变域选择,用循环语句选取一个很长的向量所有位。

6、多维数组的建立

Verilog‐1995中只允许对reg,integer和time建立一维的数组,常用于RAM,ROM的建模。Verilog‐2001中可以对net和variable建立多维数组。

7、多维数组的赋值

Verilog‐1995不允许直接访问矩阵字的某一位或某几位,必须将整个矩阵字复制到另一个暂存变量中,从暂存中访问。

Verilog‐2001可以直接访问矩阵的某一维或某几位。

8、乘方运算符

增加乘方运算(power operate),运算符是**,如果其中有一个操作数是real类型的,返回值将是real类型。两个操作数都是integer类型,返回才是integer类型。

9、自动(可重入)任务和自动(递归)函数

(1)可重入任务

任务本质上是静态的,同时并发执行的多个任务共享存储区。当某个任务在模块中的多个地方被同时调用,则这两个任务对同一块地址空间进行操作,结果可能是错误的。Verilog‐2001中增加了关键字automatic,内存空间是动态分配的,使任务成为可重入的。

(2)递归函数

10、自动宽度扩展

Verilog‐1995中对于不指定位数的位宽超过32为的总线赋高阻时,只会对低32位赋值为高阻,高位将为0。

Verilog‐2001将高阻或不定态赋值给未指定位宽的信号时,可以自动扩展到整个位宽范围。

11、常数函数

Verilog语法规定必须使用数值或常数表达式来定义向量的位宽和阵列的规模。

Verilog‐1995中要求上述表达式必须为算数操作。

Verilog‐2001中可以使用函数,成为常数函数。他的数值在编译或详细描述中被确定。

12、增加了文件输入输出操作

Verilog‐1995中在文件的输入/输出操作方面功能非常有限,文件操作经常借助于Verilog PLI(编程语言接口),通过与C语言的文件输入/输出库的访问来处理。并且规定同时打开的I/O文件数不能多于31个。

Verilog‐2001增加了新的系统任务和函数,并且规定同时打开的文件数目为230个。

热门标签